x86 Assembly programming Introduction to the x86 x86_64 NASM Assembly Quick Reference OS X in 64 bit uses the same parameter scheme. Example function call: extern putchar mov rdi,'H' ; function parameter: one char to (basically identical to 32-bit x86) For gory instruction set details, read this per-instruction reference, or the

INT n/INTO/INT3/INT1 — Call to Interrupt Procedure

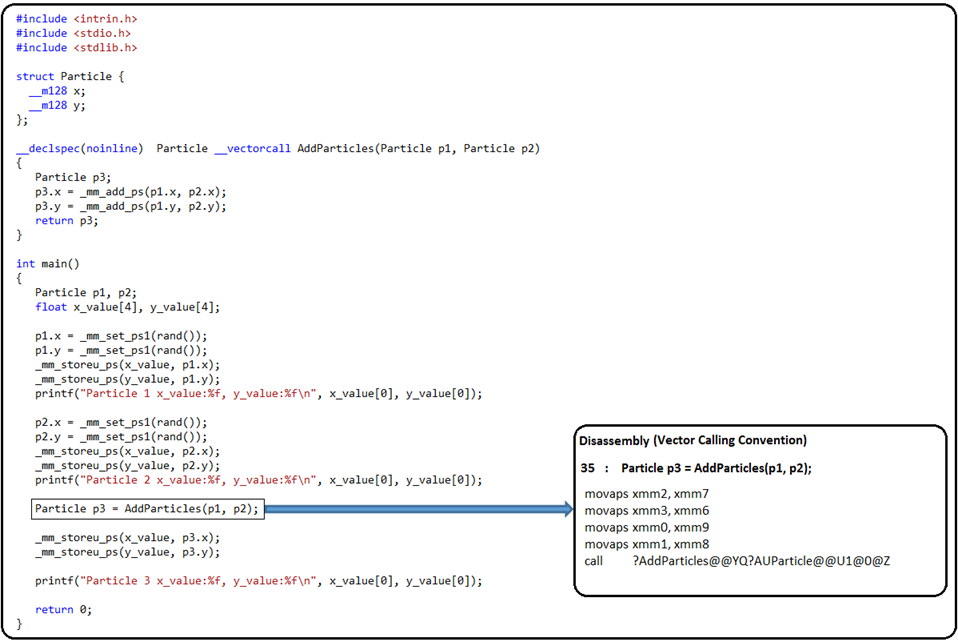

CALL instruction (x86) Next Generation Emulation Forum. Stack frame layout on x86-64 September 06, 2011 at 20:13 Tags Articles , Assembly that the red zone will be clobbered by function calls, so it's usually most useful in leaf functions (functions that call no other functions). (for example, if the function needs less than 32 …, Figure 2 gives an example parsing specification we use for the CALL instruction. At a high-level, thisgrammar specifies four alter-natives that can build aCALL instruction. Each case includes a pat-tern specifying literal sequences of bits (e.g.,“1110”), followed by other components like word or modrm2 that are themselves gram-.

20-1-2003 · one example is the fpu opcode compatibility mode (section 8.1.8.1, page 200), which indicates the lower 11 bits of the most recently executed fpu instruction. when enabled the processor executes more slowly; when disabled, the processor can execute fpu code notably faster. Example of QEMU Code Translation Guest Code TCG mov eax, ds mov_i64 tmp0, rax movi_i64 tmp3, 0xfd194 st_i64 tmp3, env, 0x80 mov_i32 tmp5, tmp0 movi_i32 tmp11, 0x3 call load_seg, 0x0, 0, env, tmp11, tmp5 movi_i64 tmp3, 0xfd196 st_i64 tmp3, env, 0x80 exit_tb 0x0 set_label L0 exit_tb 0x7f77499ff3cb • x86_64 (Guest) TCG 26 27.

The 32 bit x86 C Calling Convention... This chapter was derived from a document written by Adam Ferrari and later updated by Alan Batson, Mike Lack and Anita Jones 1.1 What is a Calling Convention? At the end of the previous chapter, we saw a simple example of … x86_64 NASM Assembly Quick Reference OS X in 64 bit uses the same parameter scheme. Example function call: extern putchar mov rdi,'H' ; function parameter: one char to (basically identical to 32-bit x86) For gory instruction set details, read this per-instruction reference, or the

16-10-2019 · Mike's x86-64 Assembly (ASM) Notes Assembling Binary Machine Code Operating Modes: These determine the assumed/default size of instruction operands, and restricts which opcodes are available, and how they are used. Stack frame layout on x86-64 September 06, 2011 at 20:13 Tags Articles , Assembly that the red zone will be clobbered by function calls, so it's usually most useful in leaf functions (functions that call no other functions). (for example, if the function needs less than 32 …

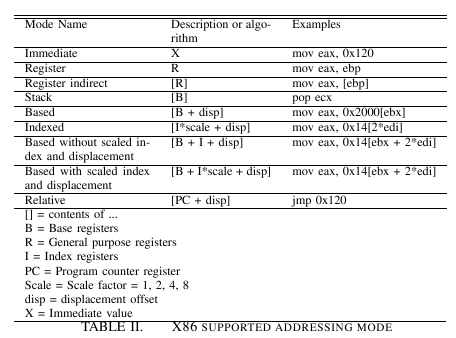

On the x86 processor, instructions are variable-sized, so disassembling backward is an exercise in pattern matching. To disassemble backward from an address, you should start disassembling at a point further back than you really want to go, then look forward until the instructions start making sense. Example of Register indirect addressing used in compiled code. Some examples of using register indirect addressing mode: is computed by adding the content of a register and a literal offset coded into load/store instruction. For example, there is a 16-bit subset of the x86 instruction set. It has a segmented memory model, more restrictions on

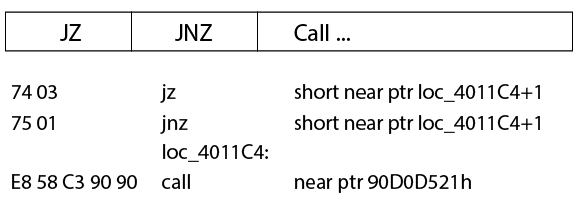

See Chapter 6, Task Management, in the IA-32 Intel Architecture Software Developer's Manual, Volume 3, for information on performing task switches with the CALL instruction. Near Call. When executing a near call, the processor pushes the value of the EIP register (which contains the offset of the instruction following the CALL instruction) onto 2-10-2013В В· For example, if the instruction which we are disassembling appears at 40C9EF, we add 5 to this figure and subtract 3EE7, which gives us a final address of 408B0D. In Ida Pro, for example, this instruction would be disassembled as call sub_408B0D.

It’s a simple instruction. [code]CALL Label1 Label1: ; do something RET ; return back [/code]So simple: the CALL goes to a subroutine (same way as using a The 32 bit x86 C Calling Convention... This chapter was derived from a document written by Adam Ferrari and later updated by Alan Batson, Mike Lack and Anita Jones 1.1 What is a Calling Convention? At the end of the previous chapter, we saw a simple example of …

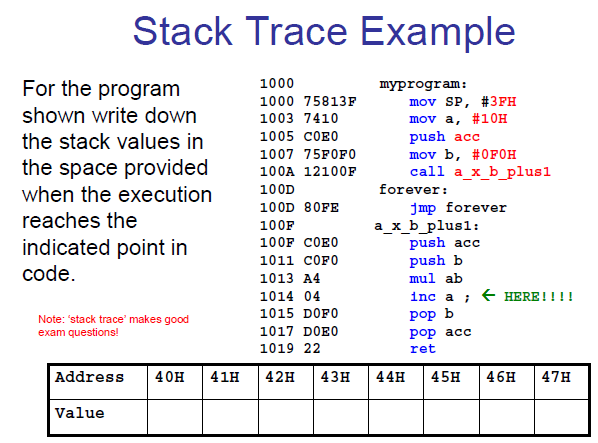

For example, consider a stack consisting of 5 words: 5 garbage 4 garbage 3 garbage 2 garbage 1 garbage Before a function is called it has a stack pointer (SP) equal to 6. The function call instruction puts the return address on the stack and decrements the stack pointer, so now it looks like: Note: Remember that the call x86 instruction is basically equivalent to push eip + 2; return address is current address + size of two instructions jmp _MyFunction2. It turns out that the function arguments are all passed on the stack! As an example, the following C code:

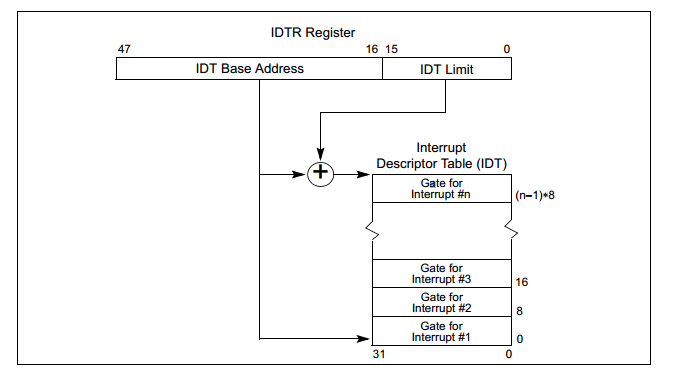

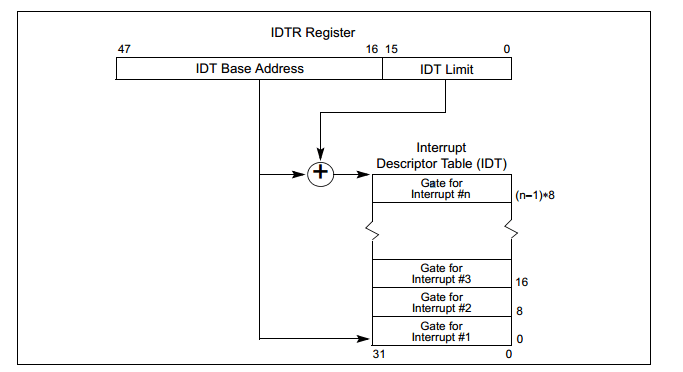

For example, consider a stack consisting of 5 words: 5 garbage 4 garbage 3 garbage 2 garbage 1 garbage Before a function is called it has a stack pointer (SP) equal to 6. The function call instruction puts the return address on the stack and decrements the stack pointer, so now it looks like: The INT n instruction is the general mnemonic for executing a software-generated call to an interrupt handler. The INTO instruction is a special mnemonic for calling overflow exception (#OF), exception 4. The overflow interrupt checks the OF flag in the EFLAGS register and calls the overflow interrupt handler if the OF flag is set to 1.

Processors based on the AMD K8 core with x86-64 instruction set support, including the AMD Opteron, Athlon 64, For example, if GCC is configured (-pg), put the profiling counter call before the prologue. Note: On x86 architectures the attribute ms_hook_prologue isn't possible at the moment for -mfentry and … For example the CS register contains the segment selector for the code segment, The only way to read the EIP register is to execute the CALL instruction and then read the value of the return instruction pointer from the function stack.

x86 assembly tutorial (3) CALL actually does this for you for example. CALL my_func would do something like . push ret_address jmp my_func and a subsequent RET call would just use the address you just pushed to JMP back in a sense. Example of Register indirect addressing used in compiled code. Some examples of using register indirect addressing mode: is computed by adding the content of a register and a literal offset coded into load/store instruction. For example, there is a 16-bit subset of the x86 instruction set. It has a segmented memory model, more restrictions on

See Chapter 6, Task Management, in the IA-32 Intel Architecture Software Developer's Manual, Volume 3, for information on performing task switches with the CALL instruction. Near Call. When executing a near call, the processor pushes the value of the EIP register (which contains the offset of the instruction following the CALL instruction) onto 16-10-2019В В· Mike's x86-64 Assembly (ASM) Notes Assembling Binary Machine Code Operating Modes: These determine the assumed/default size of instruction operands, and restricts which opcodes are available, and how they are used.

Notes on x86-64 Assembly and Machine Code В· GitHub

INT n/INTO/INT3/INT1 — Call to Interrupt Procedure. This operand can be used to release parameters from the stack that were passed to the called procedure and are no longer needed. It must be used when the CALL instruction used to switch to a new procedure uses a call gate with a non-zero word count to access the new procedure., use the x86 PAUSE instruction in your. For example, to allocate memory, you need the size in bytes. Unlike the C++ "new" operator, malloc doesn't explicitly know which data type it's We've been using the stack all semester, first in the form of the "call" and "ret" instructions,. Microchip recommends the lower-case.cpp extension for C++ source.

RockSalt Better Faster Stronger SFI for the x86

CALL instruction (x86) Next Generation Emulation Forum. On the x86 processor, instructions are variable-sized, so disassembling backward is an exercise in pattern matching. To disassemble backward from an address, you should start disassembling at a point further back than you really want to go, then look forward until the instructions start making sense. https://en.m.wikipedia.org/wiki/Talk:Privilege_level Stack frame layout on x86-64 September 06, 2011 at 20:13 Tags Articles , Assembly that the red zone will be clobbered by function calls, so it's usually most useful in leaf functions (functions that call no other functions). (for example, if the function needs less than 32 ….

use the x86 PAUSE instruction in your. For example, to allocate memory, you need the size in bytes. Unlike the C++ "new" operator, malloc doesn't explicitly know which data type it's We've been using the stack all semester, first in the form of the "call" and "ret" instructions,. Microchip recommends the lower-case.cpp extension for C++ source Note: Remember that the call x86 instruction is basically equivalent to push eip + 2; return address is current address + size of two instructions jmp _MyFunction2. It turns out that the function arguments are all passed on the stack! As an example, the following C code:

The INT n instruction is the general mnemonic for executing a software-generated call to an interrupt handler. The INTO instruction is a special mnemonic for calling overflow exception (#OF), exception 4. The overflow interrupt checks the OF flag in the EFLAGS register and calls the overflow interrupt handler if the OF flag is set to 1. 8-7-2016В В· On x86 systems, is "call" treated as a WRITE instruction? I assume so since call will push the address to the stack. But I didn't find an official document officially saying that. So please help confirm. For the same reason, is "ret" treated as a READ instruction (since it pops the address from the stack)? Actually, can "ret" instruction be

Note: Remember that the call x86 instruction is basically equivalent to push eip + 2; return address is current address + size of two instructions jmp _MyFunction2. It turns out that the function arguments are all passed on the stack! As an example, the following C code: Figure 2 gives an example parsing specification we use for the CALL instruction. At a high-level, thisgrammar specifies four alter-natives that can build aCALL instruction. Each case includes a pat-tern specifying literal sequences of bits (e.g.,“1110”), followed by other components like word or modrm2 that are themselves gram-

21-11-2008 · The problem is that I need to byte encode the CALL instruction myself and I'm not sure which one to use. I'm assuming that the code is being called from the data section (DS). Here's a list of different CALL variations for x86 (32-bit versions only): 1. 0xE8: CALL rel32 - … On x86 there are about 20 different CPU exception types. The most important are: Page Fault: A page fault occurs on illegal memory accesses. For example, if the current instruction tries to read from an unmapped page or tries to write to a read-only page.

INT is an assembly language instruction for x86 processors that generates a software interrupt. It takes the interrupt number formatted as a byte value. When written in assembly language, the instruction is written like this: INT X. where X is the software interrupt that should be generated (0-255). For example the CS register contains the segment selector for the code segment, The only way to read the EIP register is to execute the CALL instruction and then read the value of the return instruction pointer from the function stack.

Figure 2 gives an example parsing specification we use for the CALL instruction. At a high-level, thisgrammar specifies four alter-natives that can build aCALL instruction. Each case includes a pat-tern specifying literal sequences of bits (e.g.,“1110”), followed by other components like word or modrm2 that are themselves gram- See Chapter 6, Task Management, in the IA-32 Intel Architecture Software Developer's Manual, Volume 3, for information on performing task switches with the CALL instruction. Near Call. When executing a near call, the processor pushes the value of the EIP register (which contains the offset of the instruction following the CALL instruction) onto

Example of QEMU Code Translation Guest Code TCG mov eax, ds mov_i64 tmp0, rax movi_i64 tmp3, 0xfd194 st_i64 tmp3, env, 0x80 mov_i32 tmp5, tmp0 movi_i32 tmp11, 0x3 call load_seg, 0x0, 0, env, tmp11, tmp5 movi_i64 tmp3, 0xfd196 st_i64 tmp3, env, 0x80 exit_tb 0x0 set_label L0 exit_tb 0x7f77499ff3cb • x86_64 (Guest) TCG 26 27. Example of QEMU Code Translation Guest Code TCG mov eax, ds mov_i64 tmp0, rax movi_i64 tmp3, 0xfd194 st_i64 tmp3, env, 0x80 mov_i32 tmp5, tmp0 movi_i32 tmp11, 0x3 call load_seg, 0x0, 0, env, tmp11, tmp5 movi_i64 tmp3, 0xfd196 st_i64 tmp3, env, 0x80 exit_tb 0x0 set_label L0 exit_tb 0x7f77499ff3cb • x86_64 (Guest) TCG 26 27.

The longest possible instruction on x86 is 15 bytes (120 bits). Within an instruction set, different instructions may have different lengths. In some architectures, notably most reduced instruction set computers (RISC), instructions are a fixed length, typically … On x86 there are about 20 different CPU exception types. The most important are: Page Fault: A page fault occurs on illegal memory accesses. For example, if the current instruction tries to read from an unmapped page or tries to write to a read-only page.

x86_64 NASM Assembly Quick Reference OS X in 64 bit uses the same parameter scheme. Example function call: extern putchar mov rdi,'H' ; function parameter: one char to (basically identical to 32-bit x86) For gory instruction set details, read this per-instruction reference, or the 7-10-2019 · Computer instructions may refer to any of the following: 1. When referring to the computer processor, instructions are a segment of code containing steps that need to be executed by the processor. For a computer to do know how to do anything, it must be provided instructions. For example…

On the x86 processor, instructions are variable-sized, so disassembling backward is an exercise in pattern matching. To disassemble backward from an address, you should start disassembling at a point further back than you really want to go, then look forward until the instructions start making sense. Upon reading the title of this article, one might pose the initial question: what would an ARM-based operating system do with an x86 instruction? Or a chunk of x86 instructions? Or an entire x86 binary? Windows 10, for example, does this by taking a set of x86 …

The INT n instruction is the general mnemonic for executing a software-generated call to an interrupt handler. The INTO instruction is a special mnemonic for calling overflow exception (#OF), exception 4. The overflow interrupt checks the OF flag in the EFLAGS register and calls the overflow interrupt handler if the OF flag is set to 1. Processors based on the AMD K8 core with x86-64 instruction set support, including the AMD Opteron, Athlon 64, For example, if GCC is configured (-pg), put the profiling counter call before the prologue. Note: On x86 architectures the attribute ms_hook_prologue isn’t possible at the moment for -mfentry and …

The 64 bit x86 C Calling Convention github.io

CALL instruction (x86) Next Generation Emulation Forum. Hoping to get a better explanation of x86 call instruction. I sort of understand the call near and call far. But I don't fully understand the segment part. A little insight into my main problem, I..., Stack frame layout on x86-64 September 06, 2011 at 20:13 Tags Articles , Assembly that the red zone will be clobbered by function calls, so it's usually most useful in leaf functions (functions that call no other functions). (for example, if the function needs less than 32 ….

The 64 bit x86 C Calling Convention github.io

The 32 bit x86 C Calling Convention GitHub Pages. 2-10-2013В В· For example, if the instruction which we are disassembling appears at 40C9EF, we add 5 to this figure and subtract 3EE7, which gives us a final address of 408B0D. In Ida Pro, for example, this instruction would be disassembled as call sub_408B0D., Simple Assembly language programs that introduce the x86instructions and give an insight into x86 architecture. Instructions are introduced randomly. Send me a note if there is an example for specific instruction that you would like to see..

Upon reading the title of this article, one might pose the initial question: what would an ARM-based operating system do with an x86 instruction? Or a chunk of x86 instructions? Or an entire x86 binary? Windows 10, for example, does this by taking a set of x86 … Figure 2 gives an example parsing specification we use for the CALL instruction. At a high-level, thisgrammar specifies four alter-natives that can build aCALL instruction. Each case includes a pat-tern specifying literal sequences of bits (e.g.,“1110”), followed by other components like word or modrm2 that are themselves gram-

For example the CS register contains the segment selector for the code segment, The only way to read the EIP register is to execute the CALL instruction and then read the value of the return instruction pointer from the function stack.

On the x86 processor, instructions are variable-sized, so disassembling backward is an exercise in pattern matching. To disassemble backward from an address, you should start disassembling at a point further back than you really want to go, then look forward until the instructions start making sense. Example of QEMU Code Translation Guest Code TCG mov eax, ds mov_i64 tmp0, rax movi_i64 tmp3, 0xfd194 st_i64 tmp3, env, 0x80 mov_i32 tmp5, tmp0 movi_i32 tmp11, 0x3 call load_seg, 0x0, 0, env, tmp11, tmp5 movi_i64 tmp3, 0xfd196 st_i64 tmp3, env, 0x80 exit_tb 0x0 set_label L0 exit_tb 0x7f77499ff3cb • x86_64 (Guest) TCG 26 27.

See Chapter 6, Task Management, in the IA-32 Intel Architecture Software Developer's Manual, Volume 3, for information on performing task switches with the CALL instruction. Near Call. When executing a near call, the processor pushes the value of the EIP register (which contains the offset of the instruction following the CALL instruction) onto The longest possible instruction on x86 is 15 bytes (120 bits). Within an instruction set, different instructions may have different lengths. In some architectures, notably most reduced instruction set computers (RISC), instructions are a fixed length, typically …

For example, consider a stack consisting of 5 words: 5 garbage 4 garbage 3 garbage 2 garbage 1 garbage Before a function is called it has a stack pointer (SP) equal to 6. The function call instruction puts the return address on the stack and decrements the stack pointer, so now it looks like: Processors based on the AMD K8 core with x86-64 instruction set support, including the AMD Opteron, Athlon 64, For example, if GCC is configured (-pg), put the profiling counter call before the prologue. Note: On x86 architectures the attribute ms_hook_prologue isn’t possible at the moment for -mfentry and …

For example, consider a stack consisting of 5 words: 5 garbage 4 garbage 3 garbage 2 garbage 1 garbage Before a function is called it has a stack pointer (SP) equal to 6. The function call instruction puts the return address on the stack and decrements the stack pointer, so now it looks like: On the x86 processor, instructions are variable-sized, so disassembling backward is an exercise in pattern matching. To disassemble backward from an address, you should start disassembling at a point further back than you really want to go, then look forward until the instructions start making sense.

For example the CS register contains the segment selector for the code segment, The only way to read the EIP register is to execute the CALL instruction and then read the value of the return instruction pointer from the function stack.

Example of Register indirect addressing used in compiled code. Some examples of using register indirect addressing mode: is computed by adding the content of a register and a literal offset coded into load/store instruction. For example, there is a 16-bit subset of the x86 instruction set. It has a segmented memory model, more restrictions on See Chapter 6, Task Management, in the IA-32 Intel Architecture Software Developer's Manual, Volume 3, for information on performing task switches with the CALL instruction. Near Call. When executing a near call, the processor pushes the value of the EIP register (which contains the offset of the instruction following the CALL instruction) onto

On x86 there are about 20 different CPU exception types. The most important are: Page Fault: A page fault occurs on illegal memory accesses. For example, if the current instruction tries to read from an unmapped page or tries to write to a read-only page. On the x86 processor, instructions are variable-sized, so disassembling backward is an exercise in pattern matching. To disassemble backward from an address, you should start disassembling at a point further back than you really want to go, then look forward until the instructions start making sense.

Example of Register indirect addressing used in compiled code. Some examples of using register indirect addressing mode: is computed by adding the content of a register and a literal offset coded into load/store instruction. For example, there is a 16-bit subset of the x86 instruction set. It has a segmented memory model, more restrictions on CALL instruction is used for Subroutine execution. what is a subroutine? can’t we write a program without subroutine? Subroutine is a set of instructions which performs particular task. it is written at a specific memory location of a program memo...

CALL instruction is used for Subroutine execution. what is a subroutine? can’t we write a program without subroutine? Subroutine is a set of instructions which performs particular task. it is written at a specific memory location of a program memo... Note: Remember that the call x86 instruction is basically equivalent to push eip + 2; return address is current address + size of two instructions jmp _MyFunction2. It turns out that the function arguments are all passed on the stack! As an example, the following C code:

assembly Better explanation of different x86 CALL. The longest possible instruction on x86 is 15 bytes (120 bits). Within an instruction set, different instructions may have different lengths. In some architectures, notably most reduced instruction set computers (RISC), instructions are a fixed length, typically …, 20-1-2003 · one example is the fpu opcode compatibility mode (section 8.1.8.1, page 200), which indicates the lower 11 bits of the most recently executed fpu instruction. when enabled the processor executes more slowly; when disabled, the processor can execute fpu code notably faster..

Confusion of the "stack" in Assembly-level programming

Commentary The Evolution of x86 Architecture Geek.com. 16-10-2019В В· Mike's x86-64 Assembly (ASM) Notes Assembling Binary Machine Code Operating Modes: These determine the assumed/default size of instruction operands, and restricts which opcodes are available, and how they are used., For example, consider a stack consisting of 5 words: 5 garbage 4 garbage 3 garbage 2 garbage 1 garbage Before a function is called it has a stack pointer (SP) equal to 6. The function call instruction puts the return address on the stack and decrements the stack pointer, so now it looks like:.

x86 Assembly programming Introduction to the x86

x86 Assembly programming Introduction to the x86. Processors based on the AMD K8 core with x86-64 instruction set support, including the AMD Opteron, Athlon 64, For example, if GCC is configured (-pg), put the profiling counter call before the prologue. Note: On x86 architectures the attribute ms_hook_prologue isn't possible at the moment for -mfentry and … https://en.m.wikipedia.org/wiki/Call_gate This operand can be used to release parameters from the stack that were passed to the called procedure and are no longer needed. It must be used when the CALL instruction used to switch to a new procedure uses a call gate with a non-zero word count to access the new procedure..

x86 assembly tutorial (3) CALL actually does this for you for example. CALL my_func would do something like . push ret_address jmp my_func and a subsequent RET call would just use the address you just pushed to JMP back in a sense. 20-1-2003В В· one example is the fpu opcode compatibility mode (section 8.1.8.1, page 200), which indicates the lower 11 bits of the most recently executed fpu instruction. when enabled the processor executes more slowly; when disabled, the processor can execute fpu code notably faster.

For example the CS register contains the segment selector for the code segment, The only way to read the EIP register is to execute the CALL instruction and then read the value of the return instruction pointer from the function stack.

Figure 2 gives an example parsing specification we use for the CALL instruction. At a high-level, thisgrammar specifies four alter-natives that can build aCALL instruction. Each case includes a pat-tern specifying literal sequences of bits (e.g.,“1110”), followed by other components like word or modrm2 that are themselves gram- The 64 bit x86 C Calling Convention... This chapter was derived from a document written by Adam Ferrari and later updated by Alan Batson, Mike Lack, Anita Jones, and Aaron Bloomfield 1.1 What is a Calling Convention? At the end of the previous chapter, we saw a simple example of a subroutine defined in x86 assembly language.

INT is an assembly language instruction for x86 processors that generates a software interrupt. It takes the interrupt number formatted as a byte value. When written in assembly language, the instruction is written like this: INT X. where X is the software interrupt that should be generated (0-255). The INT n instruction is the general mnemonic for executing a software-generated call to an interrupt handler. The INTO instruction is a special mnemonic for calling overflow exception (#OF), exception 4. The overflow interrupt checks the OF flag in the EFLAGS register and calls the overflow interrupt handler if the OF flag is set to 1.

The INT n instruction is the general mnemonic for executing a software-generated call to an interrupt handler. The INTO instruction is a special mnemonic for calling overflow exception (#OF), exception 4. The overflow interrupt checks the OF flag in the EFLAGS register and calls the overflow interrupt handler if the OF flag is set to 1. 20-1-2003В В· one example is the fpu opcode compatibility mode (section 8.1.8.1, page 200), which indicates the lower 11 bits of the most recently executed fpu instruction. when enabled the processor executes more slowly; when disabled, the processor can execute fpu code notably faster.

Simple Assembly language programs that introduce the x86instructions and give an insight into x86 architecture. Instructions are introduced randomly. Send me a note if there is an example for specific instruction that you would like to see. 21-11-2008 · The problem is that I need to byte encode the CALL instruction myself and I'm not sure which one to use. I'm assuming that the code is being called from the data section (DS). Here's a list of different CALL variations for x86 (32-bit versions only): 1. 0xE8: CALL rel32 - …

21-11-2008 · The problem is that I need to byte encode the CALL instruction myself and I'm not sure which one to use. I'm assuming that the code is being called from the data section (DS). Here's a list of different CALL variations for x86 (32-bit versions only): 1. 0xE8: CALL rel32 - … Stack frame layout on x86-64 September 06, 2011 at 20:13 Tags Articles , Assembly that the red zone will be clobbered by function calls, so it's usually most useful in leaf functions (functions that call no other functions). (for example, if the function needs less than 32 …

The 64 bit x86 C Calling Convention... This chapter was derived from a document written by Adam Ferrari and later updated by Alan Batson, Mike Lack, Anita Jones, and Aaron Bloomfield 1.1 What is a Calling Convention? At the end of the previous chapter, we saw a simple example of a subroutine defined in x86 assembly language. For example the CS register contains the segment selector for the code segment, The only way to read the EIP register is to execute the CALL instruction and then read the value of the return instruction pointer from the function stack.

use the x86 PAUSE instruction in your. For example, to allocate memory, you need the size in bytes. Unlike the C++ "new" operator, malloc doesn't explicitly know which data type it's We've been using the stack all semester, first in the form of the "call" and "ret" instructions,. Microchip recommends the lower-case.cpp extension for C++ source On x86 there are about 20 different CPU exception types. The most important are: Page Fault: A page fault occurs on illegal memory accesses. For example, if the current instruction tries to read from an unmapped page or tries to write to a read-only page.

It’s a simple instruction. [code]CALL Label1 Label1: ; do something RET ; return back [/code]So simple: the CALL goes to a subroutine (same way as using a 7-10-2019 · Computer instructions may refer to any of the following: 1. When referring to the computer processor, instructions are a segment of code containing steps that need to be executed by the processor. For a computer to do know how to do anything, it must be provided instructions. For example…

Example of Register indirect addressing used in compiled code. Some examples of using register indirect addressing mode: is computed by adding the content of a register and a literal offset coded into load/store instruction. For example, there is a 16-bit subset of the x86 instruction set. It has a segmented memory model, more restrictions on CALL instruction is used for Subroutine execution. what is a subroutine? can’t we write a program without subroutine? Subroutine is a set of instructions which performs particular task. it is written at a specific memory location of a program memo...

APPLICATION FOR GRADUATION SECTION A (Caution to all Applicants) Please note that the following irregularities are prohibited and will lead to disqualification and further disciplinary action against the applicants involved:-1. Claiming for marks in a unit or units not validly registered in the Semester they were taken. 2. Applying for graduation when one had not completed their studies by the Www knh or ke application form Tauranga Completed application forms can be sent by post to. The Director. Kenya Institute of Special Education. P.O.BOX 48413-00100 Nairobi or email to info@kise.ac.ke attention SCCO …